# The use of silicon epitaxy in advanced n-type PERT and IBC silicon solar cell designs

María Recamán Payo¹, Izabela Kuzma-Filipek¹, Filip Duerinckx¹, Yuandong Li¹, Emanuele Cornagliotti¹, Angel Uruena¹, Loic Tous¹, Richard Russell¹, Ali Hajjiah², Maarten Debucquoy¹, Jozef Szlufcik¹ & Jozef Poortmans¹,³

<sup>1</sup>imec, Leuven, Belgium; <sup>2</sup>Kuwait University, College of Engineering and Petroleum, Electrical Engineering Dept., Safat, Kuwait; <sup>3</sup>KU Leuven, Leuven, and University of Hasselt, Diepenbeek, Belgium

#### **ABSTRACT**

This paper gives an overview of the application of silicon epitaxy as a doping technology in bulk crystalline silicon solar cells. The large degree of flexibility in designing a doped profile in one process step, and the elegant way of locally creating doped regions, or simply achieving single-side doping by selective epitaxy, are presented. Other advantages – such as the absence of subsequent steps to drive in the doped region, to activate the dopants and to heal any damage or remove glassy layers – position the technology as a strong alternative to classical diffusion. Silicon epitaxy is possible on the flat and textured surfaces of solar material, and is compatible with cleaning sequences suited to industrial implementation. The integration of epitaxial layers in solar cells is capable of providing not only high efficiencies but also simplifications of the cell fabrication process, and, therefore, reductions in the cell cost of ownership (CoO). The proof of concept at the cell level has been demonstrated by the integration of boron-doped epitaxial emitters in n-type IBC and PERT solar cells: 22.8% efficiency for IBC (4cm²) and 21.9% for PERT (238.9cm²) devices have been obtained.

#### Introduction

The epitaxial growth of silicon on crystalline material consists of the regularly oriented growth of a crystalline silicon layer upon the substrate surface, where the substrate acts as a template for the growing layer [1–2]. Silicon epitaxy is possible not only on monocrystalline but also on polycrystalline material [3]. Moreover, the process is not restricted to mirrorpolished surfaces, but is also applicable on typical Czochralski (Cz) material used in solar cell fabrication after saw-

damage removal (SDR) or anisotropic texturing [4].

The doping of the epitaxial layer takes place by in situ incorporation of the dopant source during growth. In fact, epitaxy enables a high degree of flexibility in designing a doped profile in one process step, as both the dopant concentration and the thickness of the layer can be decoupled. In addition, after epitaxy there is no need for subsequent steps to drive in the doped region, activate the dopants, heal any damage or remove glassy layers.

The selective epitaxial growth of silicon can further reduce the complexity of cell fabrication when it is applied to locally create doped regions or to simply achieve single-side doping. In selective epitaxy, the process conditions are such that the net outcome of the silicon growth is the result of a balance between silicon deposition and silicon etching upon substrates where part of the surface is 'masked' with a dielectric/dielectrics, while the rest is 'free' of dielectric(s) [5]. The overall result is the growth of a

lateral overgrowth

PSG

laser ablation patterning

selective epitaxial layer

substrate

APCVD SiO<sub>x</sub> + PECVD SiN<sub>x</sub>

wet etch patterning

selective epitaxial layer

Figure 1. SEM images: examples of selective epitaxial growth on Cz silicon solar wafers using different dielectrics.

Fab & Facilities

Materials

Cell Processing

Thin Film

PV Modules

Market Watch silicon layer solely on the areas 'free' of dielectric (Fig. 1). The dielectric can be kept after epitaxy for passivation and optical purposes, or can even serve as an additional dopant source [6].

Cell Processing

"Silicon epitaxy is capable of realizing not only high efficiencies but also simplifications of the cell fabrication process."

In sum, the aforementioned benefits place epitaxy as a strong alternative technology to classical diffusion for creating the doped regions of bulk crystalline silicon solar cells. This paper first gives an overview of the application of epitaxy to bulk crystalline silicon technology; then a proof of concept at the device level is demonstrated for solar cell concepts, such as n-type passivated emitter and rear totally diffused (PERT) and interdigitated back contact (IBC). The integration of boron-doped epitaxial emitters on the rear side of these devices demonstrates that silicon epitaxy is capable of realizing not only high efficiencies but also simplifications of the cell fabrication process, and, thus, reductions in the cell cost of ownership (CoO).

### Epitaxy on solar silicon wafers

This section begins by giving a general insight into silicon epitaxial technology; it then continues with a discussion of the impact of the substrate surface morphology, the cleaning prior to epitaxial deposition, the properties of the dielectrics used as a 'mask' during the selective deposition of silicon, and the doping profile capability of silicon epitaxy. The performance of boron-doped epitaxial emitters, used in cell concepts such as n-type IBC and PERT cells, is compared with that of reference boron-doped diffused emitters.

While not within the scope of this paper, the study is equally applicable to phosphorus-doped epitaxial layers.

#### Silicon epitaxy

In this work, the epitaxial growth of silicon is realized by chemical vapour deposition (CVD): the deposition of the silicon layer takes place by means of chemical reactions and surface absorption through a gaseous phase [1-2]. The process described herein takes place at a reduced pressure (<100Torr) and a temperature between 850 and 950°C. Dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>) is used as the silicon source and hydrogen (H<sub>2</sub>) as the carrier gas; however, it is also possible to use other precursors, such as silane or higher-order silanes (disilane, neopentasilane, etc.), or even organic precursors (triethoxysilane, tetramethylorthosilicate, etc.), if a lower process temperature (≤700°C) is required [7]. Diborane (B<sub>2</sub>H<sub>6</sub>) is employed as the dopant source, but other p-type and n-type sources are also available (BCl<sub>3</sub>, PH<sub>3</sub>, AsH<sub>3</sub>, etc.).

Hydrogen chloride (HCl), which is a silicon-etching agent, is formed as a by-product of the deposition from SiH<sub>2</sub>Cl<sub>2</sub>. In the selective epitaxial growth of silicon, which is a balance between a simultaneous silicon deposition and etching, the HCl resulting from the SiH<sub>2</sub>Cl<sub>2</sub>

decomposition may be sufficient to maintain selectivity; on occasion, however, additional HCl needs to be supplied to the main stream for a selective growth [5] to take place. The growth rate for a selective epitaxial process is lower than that for a non-selective process, where no silicon etching occurs and a blanket silicon layer is deposited over the entire exposed surface.

The basic steps of an epitaxial process are temperature ramp-up, hydrogen bake, silicon deposition and cool-down. The hydrogen bake, taking place before the actual deposition step, is a critical step which assists overall in the growth of a high-quality epitaxial layer. One of the main goals of the hydrogen bake is to remove native oxide from the substrate surface by hydrogen reduction. If the native oxide were not removed, the deposition would lead to a highly defective epitaxial layer or a polycrystalline layer, or, in the case of selective growth, little or no deposition. In addition to the native oxide removal, the bake can also assist in annealing crystal damage and cause a desirable surface reconstruction, providing a region near the silicon surface which is free of oxygen [1-2]. There is a suitable trade-off between bake temperature, pressure and time in order to achieve a reduced surface defectiveness. The bake temperature has a key role, and, typically, higher bake temperatures result in lower defect densities. A process occurring at a reduced pressure also tends to provide a lower crystal defect component than a process at atmospheric pressure. The specific conditions also depend on the oxygen and moisture levels inside the reaction chamber [8].

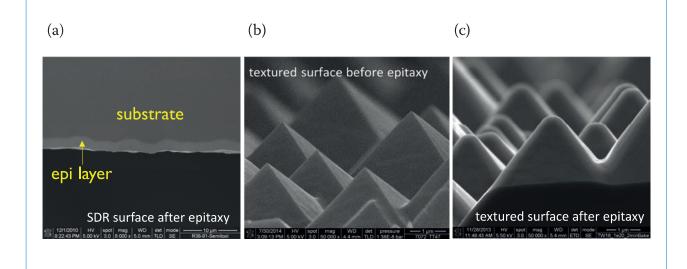

Figure 2. SEM images: (a) epitaxial layer grown on a KOH-SDR (saw-damage removal) silicon surface; (b) KOH-textured surface before epitaxy; (c) epitaxial layer grown on a KOH-textured surface.

Cell Processing

The boron-doped epitaxial emitters described here have doping levels in the range  $10^{18} - 10^{20} \text{cm}^{-3}$  and thicknesses of  $\leq 1 \mu \text{m}$ . The growth rate for these layers ranges between 30 and 750nm/min, which depends not only on the process temperature but also on the possibility of performing a blanket or selective deposition.

#### **Substrate surface morphology**

The growth of epitaxial emitters can be realized on the rough surfaces resulting from an SDR process and on the random pyramidal surfaces following an anisotropic texturing process (Fig. 2). The growth of epitaxial layers on those surfaces requires an optimization of the growth conditions and, in a very particular way, an optimization of the bake conditions prior to the actual deposition step.

At the reduced pressure (<100Torr) and the temperature range (850–950°C) normally used to grow these boron-doped epitaxial emitters, a hydrogen bake of at least 2–5min is recommended in order to achieve a sufficient epitaxial quality on both flat and textured surfaces (Fig. 2). In those conditions, a measured total defect density of less than 10<sup>4</sup> defects/cm<sup>2</sup> in the boron-doped epitaxial emitters is confirmed to be sufficient for good performance at the solar cell level.

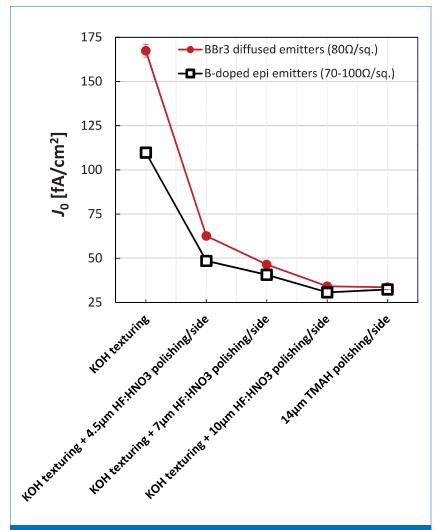

An investigation [9] of the influence of the substrate surface morphology (Fig. 3) demonstrates that an inline single-side chemical etching process based on HF:HNO $_3$  chemistry and realized on KOH-based textured surfaces can lead to values of dark-saturation current density ( $J_0$ ) as low as those measured on surfaces resulting from an SDR process based on TMAH (14µm Si removal/side). In addition, the epitaxial emitters on textured surfaces produce  $J_0$  values even lower than those using boron diffusion (see Fig. 3).

The better performance of the epitaxial emitter can be attributed to the rounding of the pyramid tips as a result of differences in crystal orientation between the pyramid planes and the peaks and valleys. The pyramid planes have a (111) crystal orientation, while at the peaks and valleys the orientation may be (100) or (110). The {111} planes present the highest packing density, which causes a slower growth rate during silicon epitaxy than on the other planes. The consequence is a thicker emitter on the pyramid tips and, therefore, a rounding of that surface compared with the pyramid planes (see Fig. 2). In the scenario where very thick epitaxial layers are grown, these differences

Figure 3.  $J_0$  (extracted at  $10^{16} {\rm cm}^{-3}$ ) for boron-doped epitaxial emitters and BBr<sub>3</sub>-diffused emitters passivated with wet oxide ( $\rho_{\rm n-type} = 3.1 \Omega \cdot {\rm cm}$ ) as a function of the substrate surface morphology.

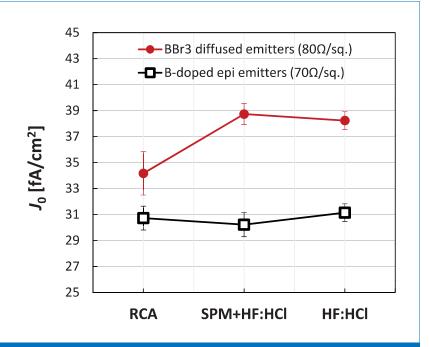

Figure 4.  $J_0$  (extracted at  $10^{16} {\rm cm}^{-3}$ ) for boron-doped epitaxial emitters and BBr<sub>3</sub>-diffused emitters passivated with wet oxide ( $\rho_{\rm n-type} = 3.1\Omega {\cdot} {\rm cm}$ ) as a function of the cleaning method prior to doping.

could lead to a planarization of the original pyramidal surfaces.

As with diffusion, the growth of high-

Ex situ cleaning

Cell

**Processing**

quality epitaxial emitters requires the removal of any particles and organic and metallic contamination from the silicon surface prior to the doping process. Wet chemical processes are normally used for the ex situ cleaning. A  $J_0$  study [9] of the performance of the boron-doped epitaxial layers revealed that the technology is compatible with cleaning sequences suited to industrial implementation in PV, such as a simple HF:HCl sequence.  $J_0$  values of around 30fA/cm<sup>2</sup> were measured (Fig. 4) for boron-doped epitaxial emitters  $(\sim 70\Omega/\text{sq.})$  passivated with a thermally grown oxide, irrespective of the type of cleaning (RCA, SPM+HF:HCl and

HF:HCl only) prior to the investigated

doping process. The BBr<sub>3</sub> diffused

emitter ( $\sim 80\Omega/\text{sq.}$ ) also included in this investigation did not perform

as well as the epitaxial emitter. In

view of these results, 'new' cleaning chemistries – such as those based on the use of ozone as the main oxidizer – have also been successfully implemented and adopted as the reference process. With this line of approach, equivalent  $J_0$  values have been measured when SOM ( $H_2SO_4$ : $O_3$  mixture) is used instead of SPM ( $H_2SO_4$ : $H_2O_2$  mixture).

#### Dielectrics and selective epitaxy

The selective deposition of silicon on Cz solar silicon wafers can be realized using a 'mask' consisting of a dielectric, or a stack of dielectrics which are of interest in PV applications: chemical vapour deposition (CVD)  $SiO_x/SiO_xN_y/SiN_x$ , atomic layer deposition (ALD)  $Al_2O_3$ , phosphosilicate glass (PSG), borosilicate glass (BSG) or thermal  $SiO_2$ . The patterning of those dielectrics prior to selective epitaxy can be performed using laser etching as well as wet or dry etching processes (see Fig. 1) [9]. Selective epitaxy

provides an elegant approach to obtaining locally doped features or single-side doping, since those layers used as a 'mask' to guarantee selective growth can be retained after epitaxy for optical and passivation purposes.

"Selective epitaxy provides an elegant approach to obtaining locally doped features or single-side doping."

Dielectrics such as plasma-enhanced chemical vapour deposition (PECVD)  $\mathrm{SiO}_{x}$  exhibit excellent passivating properties directly after emitter formation by selective epitaxy (Table 1); this results from a post-deposition annealing of the dielectric layer taking place during emitter formation by selective epitaxy. This annealing increases the structural order of

| After PECVD SiO <sub>x</sub> deposition |                        | SiO <sub>x</sub> deposition | T epitaxy [°C] | After epitaxy       |                     |  |

|-----------------------------------------|------------------------|-----------------------------|----------------|---------------------|---------------------|--|

|                                         | $	au_{	ext{eff}}$ [µs] | $J_0$ [fA/cm <sup>2</sup> ] |                | $	au_{ m eff}$ [µs] | $J_0$ [fA/cm $^2$ ] |  |

|                                         | ~10                    | -                           | 850            | 1360                | 9.3                 |  |

|                                         |                        |                             | 950            | 1750                | 11.6                |  |

Table 1. Effective lifetime  $\tau_{\rm eff}$  (at  $10^{15} {\rm cm}^{-3}$ ) and dark-saturation current density  $J_0$  (at  $10^{16} {\rm cm}^{-3}$ ) for a symmetric structure: PECVD SiO<sub>x</sub> (19nm)/n-type diffused region (310 $\Omega/{\rm sq}$ .)/n-type Cz wafer (KOH-texturing, 3.9 $\Omega\cdot{\rm cm}$ )/n-type diffused region (310 $\Omega/{\rm sq}$ .)/PECVD SiO<sub>x</sub> (19nm).

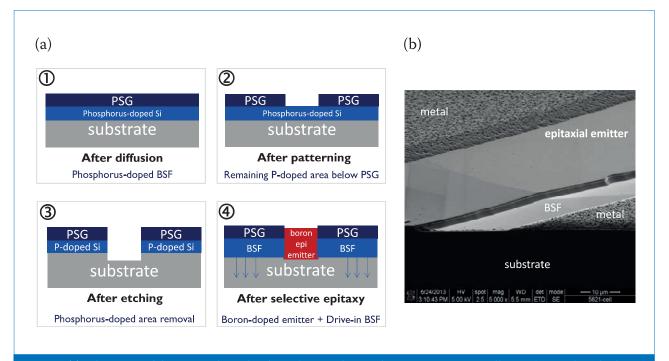

Figure 5. (a) Schematics of the approach used to form the interdigitated junction in an IBC cell using boron-doped selective epitaxy to PSG. (b) SEM image of the final layout of the interdigitated junction in an IBC cell created using this approach.

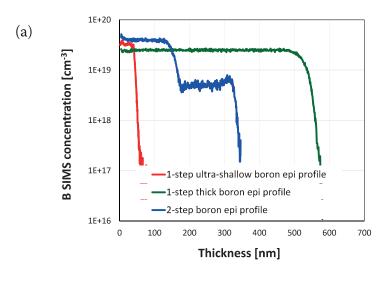

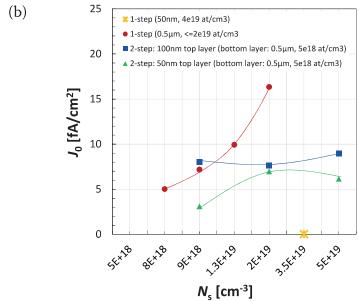

Figure 6. (a) Examples of one-step and two-step boron-doped epitaxial profiles. (b)  $I_{0,\mathrm{pass}}$  (extracted at  $10^{16}\mathrm{cm}^{-3}$ ) for boron-doped epitaxial profiles. (c) i $V_{\mathrm{oc}}$  for boron-doped epitaxial profiles.

the dielectric layer and therefore its quality, as observed by IR spectroscopy [10–11] and lifetime measurements by PL-QSSPC (Table 1).

During selective epitaxy, doped dielectrics can be used as a 'mask' too. The advantage here is that the thermal budget associated with the epitaxial process can drive the dopant source into the silicon regions 'masked' by the doped dielectric, while the growth of an epitaxial layer takes place simultaneously in the areas 'free' of dielectric [6]. A specific case of this application has been developed to create the interdigitated rear junction of an IBC cell [9]. Here, a short, lowtemperature POCl<sub>3</sub> diffusion was carried out to create an approximately 20nm-thick PSG layer, which, after patterning, was used as a 'mask' for the selective growth of the borondoped epitaxial emitter in the areas 'free' of PSG. While the emitter growth is taking place, a further phosphorus drive-in from the PSG creates the final back-surface field (BSF) profile, with the interdigitated junction of these IBC cells being formed after the selective epitaxial step (Fig. 5).

#### Advanced doping profiles

The doping flexibility of epitaxy in a single process step brings the possibility of creating doped regions with a wide variety of uniform boxtype profiles by changing the gas flows, modifying the precursors, or adapting the deposition time, temperature and pressure. Ultra-shallow (≤100nm) and thick (≥500nm) one-step as well as two-step boron-doped profiles, passivated with the stack ALD Al<sub>2</sub>O<sub>3</sub> (10nm)/PECVD SiO<sub>x</sub> (120nm), and with a sufficient surface concentration  $(N_s)$  for good ohmic contact with sputtered AlSi 1%, have demonstrated high performance in terms of recombination losses (Fig. 6) [11]. Several one-step and two-step profiles of around 500nm have provided  $J_0$ values and implied  $V_{\rm oc}$  values at 1 Sun  $(\mathrm{i} V_{\mathrm{oc}})$  in the range  $4{-}10\mathrm{fA/cm^2}$  and 725-745mV respectively [11]. Values of  $J_0 < 1 \text{fA/cm}^2$  and  $iV_{oc} = 754 \text{mV}$ have also been measured for an ultrashallow and very heavily doped layer  $(50\text{nm}, 4\cdot10^{19}\text{cm}^{-3})$ , where the fieldeffect passivation is the dominant mechanism [12].

#### N-type cells with a borondoped epitaxial emitter

#### **IBC** cells

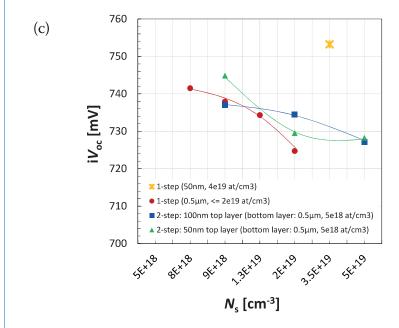

In a first approach, represented in Fig. 7(c) as 'Route A', selective epitaxy was implemented to create

Figure 7. (a) Schematic of an IBC cell. (b) Reference IBC flow with a BBr<sub>3</sub>-diffused emitter. (c) IBC flow ('Route A') with a boron-doped emitter grown by selective epitaxy to PSG.

|                                    |         | $J_{ m sc}$ [mA/cm $^2$ ] | V <sub>oc</sub> [mV] | FF [%]     | η [%]      |

|------------------------------------|---------|---------------------------|----------------------|------------|------------|

| Diffused baseline flow (reference) | Average | 41.5 ± 0.3                | 684 ± 3              | 80.3 ± 0.5 | 22.8 ± 0.4 |

|                                    | Best    | 41.7                      | 686                  | 80.7       | 23.1       |

| Flow with epi                      | Average | 41.8 ± 0.1                | 684 ± 1              | 79.1 ± 0.6 | 22.6 ± 0.2 |

| emitter ('Route A')                | Best    | 41.9                      | 686                  | 79.5       | 22.8       |

Table 2. Light I-V results for IBC cells (4cm<sup>2</sup>) fabricated using the reference flow (Fig. 7(b)) and 'Route A' with an epitaxial emitter (Fig. 7(c)).

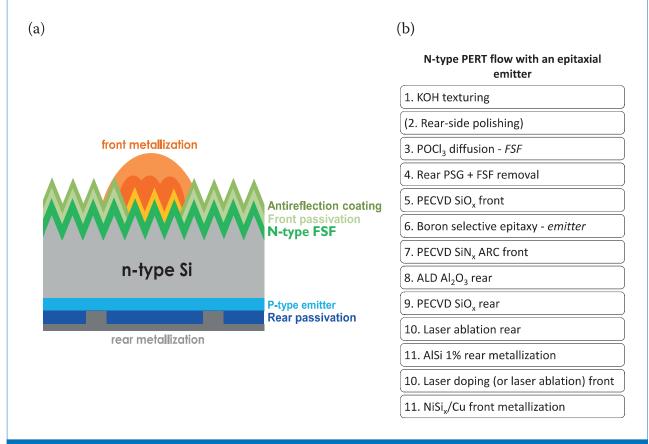

Figure 8. (a) Schematic of an n-type PERT cell. (b) N-type PERT flow with an epitaxial emitter.

| Cell       |

|------------|

| Processing |

| Epitaxial emitter                                   |         | J <sub>sc</sub> [mA/cm <sup>2</sup> ] | V <sub>oc</sub> [mV] | FF [%]         | η [%]          |  |

|-----------------------------------------------------|---------|---------------------------------------|----------------------|----------------|----------------|--|

| @ 850°C, 500nm, 9·10 <sup>18</sup> cm <sup>-3</sup> | Average | 39.7 ± 0.1                            | 685 ± 1.6            | $78.9 \pm 0.8$ | $21.5 \pm 0.3$ |  |

|                                                     | Best    | 39.7                                  | 687                  | 80.1           | 21.9           |  |

Table 3. Light I-V results for the n-type PERT cells (238.9cm<sup>2</sup>) fabricated using the flow in Fig. 8(b) with an epitaxial emitter grown on a flat rear surface. Front side: shallow (280nm) diffused FSF below the dielectric, and deep ( $\sim$ 2 $\mu$ m) laser-doped region below the metal contact.

|               |         | J <sub>sc</sub> [mA/cm <sup>2</sup> ] | V <sub>oc</sub> [mV] | FF [%]         | η [%]          |

|---------------|---------|---------------------------------------|----------------------|----------------|----------------|

| Rear flat     | Average | 39.2 ± 0.1                            | 664 ± 1              | $79.8 \pm 0.2$ | 20.8 ± 0.1     |

|               | Best    | 39.1                                  | 666                  | 80.1           | 20.9           |

| Rear textured | Average | 39.3 ± 0.1                            | $660 \pm 0$          | $79.3 \pm 0.4$ | $20.6 \pm 0.2$ |

|               | Best    | 39.5                                  | 661                  | 79.9           | 20.8           |

Table 4. Light I-V results for the n-type PERT cells (238.9cm<sup>2</sup>) fabricated using the flow in Fig. 8(b) with an epitaxial emitter (500nm,  $2 \cdot 10^{19} \text{cm}^{-3}$ ) grown on flat and textured surfaces. Front side: non-optimized, homogeneous diffused FSF (400nm) below the dielectric and the metal contact (contact patterning by laser ablation).

the interdigitated junction of n-type IBC cells (Fig. 7(a)) using the PSG formed during the POCl<sub>3</sub> diffusion of the BSF as a 'mask' in the selective deposition of the emitter (Fig. 5) [9]. This route, with an epitaxial emitter, directly simplifies the fully diffused reference flow (Fig. 7(b)) by enabling a 40% reduction in the total diffusion and oxidation processing time as well as by omitting some cleaning steps. The main I-V results of the first  $4 \text{cm}^2$ IBC cells manufactured on 156cm<sup>2</sup> Cz silicon solar wafers are summarized in Table 2. The results confirm best cell efficiencies of up to 22.8% for the IBC flow with a selective epitaxial emitter; this value is close to the efficiency of 23.1% for the more complex reference flow with a diffused emitter.

## "The results confirm best cell efficiencies of up to 22.8% for the IBC flow with a selective epitaxial emitter."

The high potential of selective epitaxy to simplify the IBC flow while keeping a high-efficiency performance opens up new possibilities for redefining a simpler fabrication sequence for this type of device and, hence, for reducing the cell CoO [13].

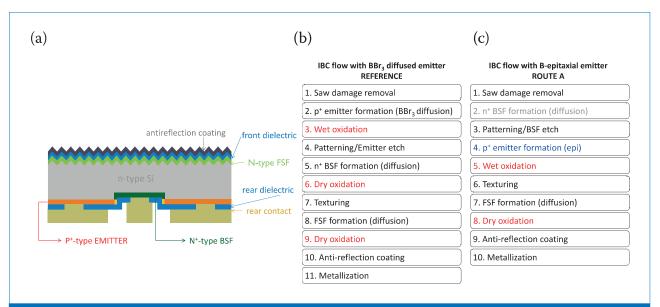

#### **PERT cells**

The route for fabricating n-type PERT cells with a boron-doped epitaxial emitter (Fig. 8) relies on single-side processing for the rear-emitter

formation by selective epitaxy, and on the dielectric deposition of a PECVD  $SiO_x/SiN_x$  stack on the front side and an ALD  $Al_2O_3/PECVD$   $SiO_x$  stack on the rear. This approach allows a single-side rear emitter, as selectivity is ensured by the presence of the PECVD  $SiO_x$  on the front side. After emitter formation, the PECVD  $SiO_x$  can be used as an excellent passivating layer of the n-type front-surface field (FSF) of these devices (see Table 1) [4,11,14].

The I-V results for the first n-type PERT cells fabricated using a half-micron-thick epitaxial emitter and a laser-doped front-side metallization scheme are summarized in Table 3. Best cell efficiencies of up to 21.9% (238.9cm²) were measured for an emitter with a uniform doping of  $9\cdot10^{18} {\rm cm}^{-3}$ .

Although the main focus has been the proof of concept for an n-type PERT solar cell with a flat rear side, epitaxy can also be applied to textured surfaces [4]. The fabrication of n-type PERT solar cells with both flat and textured rear sides, a non-optimized homogeneous diffused FSF and a laserablated front metallization scheme [14] confirms the high potential of the approach with an epitaxial emitter on textured surfaces. Both flat and textured surfaces yield comparable cell efficiencies - for the latter, they are 0.1-0.2% abs. lower (Table 4). This difference is due mainly to a drop in  $V_{\rm oc}$  of around 5mV. In-house cell CoO calculations confirm that the slightly higher efficiency for a flat rear surface does not offset the reduction in CoO resulting from the omission of the rear-side polishing.

#### **Epitaxial reactor**

The growth of the epitaxial layers in this work was accomplished in a single-wafer batch reactor, which, although sufficient for R&D purposes, is not a satisfactory solution for a production line. Actually, the tool concept which would deliver the required industrial throughput for the growth of thin epitaxial layers for PV applications is a tubular hotwall reactor [15-17], for which there are designs capable of realizing the loading of 1200 solar wafers per process chamber [18]. With these systems the CVD process is normally performed at a reduced pressure and at a temperature ranging between 400 and 900°C. In these conditions, the operation is in the kinetically limited regime, where the growth rate is exponentially dependent upon the temperature, which is very accurately controlled.

At the reduced pressure, the gas diffusivity is significantly increased compared with the values at atmospheric pressure. The net effect is a greater than one order of magnitude increase in the gasphase transfer of reactants to, and by-products from, the substrate surface. Systems operating at reduced pressure can therefore benefit from the following aspects: 1) surface kinetic control is readily achieved; 2) wafers can be vertically stacked and packed very close together; 3) little or no carrier gas is required; 4) epitaxially grown layers feature a better step coverage, conformality and a lower defect density; and 5) deposits Cell Processing

on the hot-wall reactors adhere very well and tend not to flake off.

In theory, there are no differences in process and performance between horizontal and vertical hot-wall reactors. Nevertheless, experience has proved the superiority of the vertical design because of practical reasons, such as its more compact layout; therefore the technological improvements have been historically first designed for, and implemented in, vertical furnaces.

With respect to the CoO for the tool, not enough experience has so far been gained in PV to have clear figures for a system dedicated to growing thin epitaxial layers ( $\leq 1\mu m$ ) for bulk crystalline silicon solar cells. Epitaxy is not a technology currently employed in the PV industry, and most of the existing knowledge has been acquired from microelectronics.

The CoO calculations for an epitaxial reactor will depend on the specific tool design, the process conditions (including deposition temperature), the precursors and the carrier gas. All these variables will also determine the final load per batch as well as the growth rate. Compared with a BBr3 diffusion process, for which the CoO is typically in the range €0.05-0.07/wafer, the CoO for a furnace dedicated to the growth of boron-doped thin epitaxial layers could be in the range €0.08–0.13/wafer. The difference arises mainly from a larger investment cost (CAPEX) for an epitaxial furnace.

The data used in the CoO calculations for an epitaxial furnace have their main origin in a microelectronics setting, where the specifications are more stringent than in PV, because of the need to work in a cleanroom environment and the micro- and nanoscale dimension of the devices in this field. A reduction in the investment costs for a system dedicated to PV could therefore be envisaged, as this system could be designed in more relaxed terms than one for microelectronics. Furthermore, it should also be taken into account that with epitaxy there is no need for subsequent steps, such as BSG removal or the usual boron drive-in, which engender a reduction in the cell CoO. In general, once the first tool exists, and taking into consideration the learning curve, a tendency towards lower figures should be expected for the CoO of an epitaxial PV furnace. Experience should bring down the costs, as long as the process becomes as mature and developed as the wellestablished diffusion process.

#### **Conclusions**

This paper has presented an overview of the application of silicon epitaxy as a doping technology in bulk crystalline silicon solar cells. A general picture was first given of the process conditions for the growth of epitaxial layers on the typical flat and textured surfaces used in solar cells fabrication, as well as of the cleaning before epitaxy. This was followed by a description of the advantages in terms of performance and simplifications associated with the large degree of flexibility in designing a broad range of doping profiles, and with the use of selective epitaxy to create locally doped regions.

"Epitaxy technology is a powerful alternative to classical diffusion for creating the doped regions of bulk crystalline silicon solar cells."

Finally, the proof of concept at cell level was demonstrated by the growth of boron-doped epitaxial emitters in n-type IBC and PERT solar cells: 22.8% efficiency for IBC  $(4 \text{cm}^2)$  and 21.9% for PERT  $(238.9 \text{cm}^2)$  solar cells with a  $0.5 \mu \text{m}$  boron-doped epitaxial emitter have been achieved. These results prove that epitaxy technology is a powerful alternative to classical diffusion for creating the doped regions of bulk crystalline silicon solar cells.

#### References

- [1] Herring, R.B. 1990, "Silicon Epitaxy", in *Handbook of* Semiconductor Silicon Technology. Los Altos, California, USA: Noyes Publications, pp. 258–346.

- [2] Crippa, D. et al. (Eds) 2001, Silicon Epitaxy (Semiconductors and Semimetals Series, Vol. 72). San Diego, California, USA: Academic Press.

- [3] Recamán Payo, M. et al. 2010, "Screen-printing process on 20 micron thick epitaxial UMG multicrystalline-Si solar cells (efficiencies up to 14.5 %)", Proc. 25th EU PVSEC, Valencia, Spain, pp. 3646–3650.

- [4] Recamán Payo, M. et al. 2014, "Opportunities for silicon epitaxy in bulk crystalline silicon photovoltaics", *Proc. 29th EU PVSEC*, Amsterdam, The Netherlands, pp. 497–502.

- [5] Goulding, M.R. 1993, "The selective epitaxial growth of

- silicon", *Mater. Sci. Eng. B*, Vol. 17, pp. 47–67.

- [6] Recamán Payo, M. et al. 2013, "Method for forming patterns of differently doped regions", Patent WO 2013/020868 A1.

- [7] Chung, K.H. 2008, 'Ultrahigh growth rate of epitaxial silicon by chemical vapor deposition at low temperature with neopentasilane', *Appl. Phys. Lett.*, Vol. 92, pp. 113506-1–113506-3.

- [8] Smith, F.W. et al. 1982, "Reaction of oxygen with Si(111) and (100): Critical conditions for the growth of SiO<sub>2</sub>", *J. Electrochem. Soc.*, Vol. 129, No. 6, pp. 1300–1306.

- [9] Recamán Payo, M. et al. 2013, "Boron-doped selective silicon epitaxy: High efficiency and process simplification in interdigitated back contact cells", Prog. Photovoltaics Res. Appl., Vol. 22, No. 4, pp. 711–725.

- [10] Bensch, W. et al. 1990, "An FT-IR study of silicon dioxides for VLSI microelectronics", *Semicond. Sci. Technol.*, 5, pp. 421–428.

- [11] Recamán Payo, M. et al. 2015, "Advanced doping profiles by selective epitaxy in n-type PERT cells", submitted for the 30th EU PVSEC, Hamburg, Germany.

- [12] Zhong, S. et al. 2013, "Simulation of high-efficiency crystalline silicon solar cells with homohetero junctions", *IEEE Trans. Electron Dev.*, Vol. 60, No. 7, pp. 2104–2110.

- [13] Li, Y. et al. 2015, "Process simplification and improvement of rear side of IBC cells by means of PECVD SiO<sub>x</sub> and epitaxy", submitted for the 30th EU PVSEC, Hamburg, Germany.

- [14] Kuzma-Filipek, I. 2015, "Integration processes for nPERT Si solar cells using single-side emitter epitaxy and front side laser doping", Proc. 5th SiliconPV, Konstanz, Germany.

- [15] Ritter, G. et al. 2000, "Low temperature Si epitaxy in a vertical LPCVD batch reactor", *Mater. Sci. Eng. B*, Vol. 73, pp. 203–207.

- [16] Naumann, A. et al. 2011, "SiGe epitaxy on a 300 mm batch furnace", J. Nanosci. Nanotechnol., Vol. 11, pp. 8040–8043.

- [17] Naber, R. et al. 2015, "Doping techniques and process integration solutions for n-type solar cells", 5th nPV Workshop, Konstanz, Germany.

- [18] De Ridder, C.G.M. et al. 2012, "Method for processing solar cell substrates", Patent US 8338210 B2.

Cell Processing

#### **About the Authors**

María Recamán Payo received her degree in chemical engineering from the University of Santiago de Compostela in 2002, followed by her Ph.D. from the Complutense University of Madrid in 2008. She then joined imec, where she is currently working as a senior scientist on the application of silicon CVD processes in bulk crystalline silicon solar cells.

Izabela Kuzma-Filipek has been working as a senior scientist in the silicon photovoltaics group at imec since 2009. She received her master's in materials science and ceramics from the AGH Cracow, Poland, in 2004, followed by her Ph.D. in 2010 from KU Leuven, Belgium. Her current focus is on integration processes for n-type PERx silicon solar cells with conventional and epitaxial emitters.

**Filip Duerinckx** leads the iPERx platform in the silicon photovoltaics group at imec. He received his Master of Science in engineering in 1994 from KU Leuven, Belgium, followed by his Ph.D. in 1999. He currently focuses on the performance and economical aspects of n-type PERx silicon solar cells.

Yuandong Li received a master's in electronics engineering in 2013 from Zhejiang University, Hangzhou, China. Since 2013 he has been at KU Leuven and imec in Belgium, working towards his Ph.D., with a focus on highefficiency silicon wafer solar cells using selective epitaxial doping technology.

**Emanuele Cornagliotti** received his M.Sc. in 2006 from the Polytechnic University of Turin, Italy, and his Ph.D. in 2011 in electrical and electronic engineering from KU Leuven, Belgium. Since 2007 he has been working as

a researcher at imec, where he is involved with the development of industrial silicon solar cells, with a focus on process integration.

Angel Uruena is a silicon PV research scientist at imec, where he focuses on the development of n-type solar cells. He obtained a B.Sc. in telecommunications and an M.Sc. in electronics in 2004 and 2007 respectively, from the University of Valladolid. He received his Ph.D. in electrical engineering from KU Leuven in 2013.

Loic Tous received an M.Sc. (Eng.) in material science and engineering from INSA Lyon, France, in 2009, and a Ph.D. in electrical engineering from KU Leuven, Belgium, in 2014. Since 2014 he has been a PV researcher at imec, working on nickel/copper plated contacts.

Richard Russell received a bachelor's in physics from the University of Exeter, England, and a master's degree in physics from the University of Dundee, Scotland. Between 1990 and 2010 he worked for BP Solar, mainly on Ni/Cu-metallized laser-grooved buried contact cells. He joined imec in 2011, where he leads copper-based metallization activities within the iPERx platform.

Ali Hajjiah graduated with a B.Sc. in electrical engineering from Oklahoma State University, USA, in 1998, and subsequently earned M.Sc. and Ph.D. degrees, in 2003 and 2009 respectively, from Virginia Tech, USA. His research interests lie in III-V semiconductor lasers and solar cells. He is currently an assistant professor in the electrical engineering department at Kuwait University.

Maarten Debucquoy received a Master of Science in engineering from KU Leuven, Belgium, in 2003. Following a postgraduate study in business economics in 2004, he received his Ph.D. in 2009. He then joined the photovoltaics department at imec, where he has led the activities concerning IBC silicon solar cells since 2013.

Jozef Szlufcik received his M.Sc. and Ph.D. degrees, both in electronic engineering, from the Wroclaw University of Technology, Poland. In 1990 he joined imec, where he led research activities in low-cost crystalline silicon solar cells. From 2003 to 2012 he held the position of R&D and technology manager at Photovoltech, Belgium, and is currently the director of the photovoltaics department at imec.

Jozef Poortmans received his degree in electronic engineering from KU Leuven, Belgium, in 1985, and his Ph.D., with a focus on strained SiGe layers, in June 1993. He is currently the scientific director of PV activities at imec and a member of the steering committee of the EU PV Technology Platform. Since 2008 he has been a part-time professor at KU Leuven, and in 2013 became an imec Fellow and part-time professor at the University of Hasselt.

#### **Enquiries**

Maria Recamán Payo imec Kapeldreef 75 B-3001 Leuven Belgium

Tel: +32 1628 1478 Email: Maria.RecamanPayo@imec.be